Noticias

Primeras imágenes del procesador Intel Sapphire Rapids Xeon, es enorme

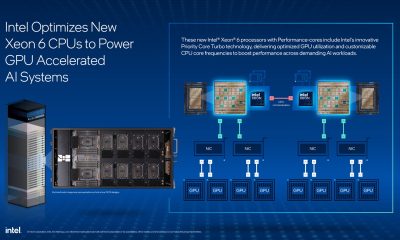

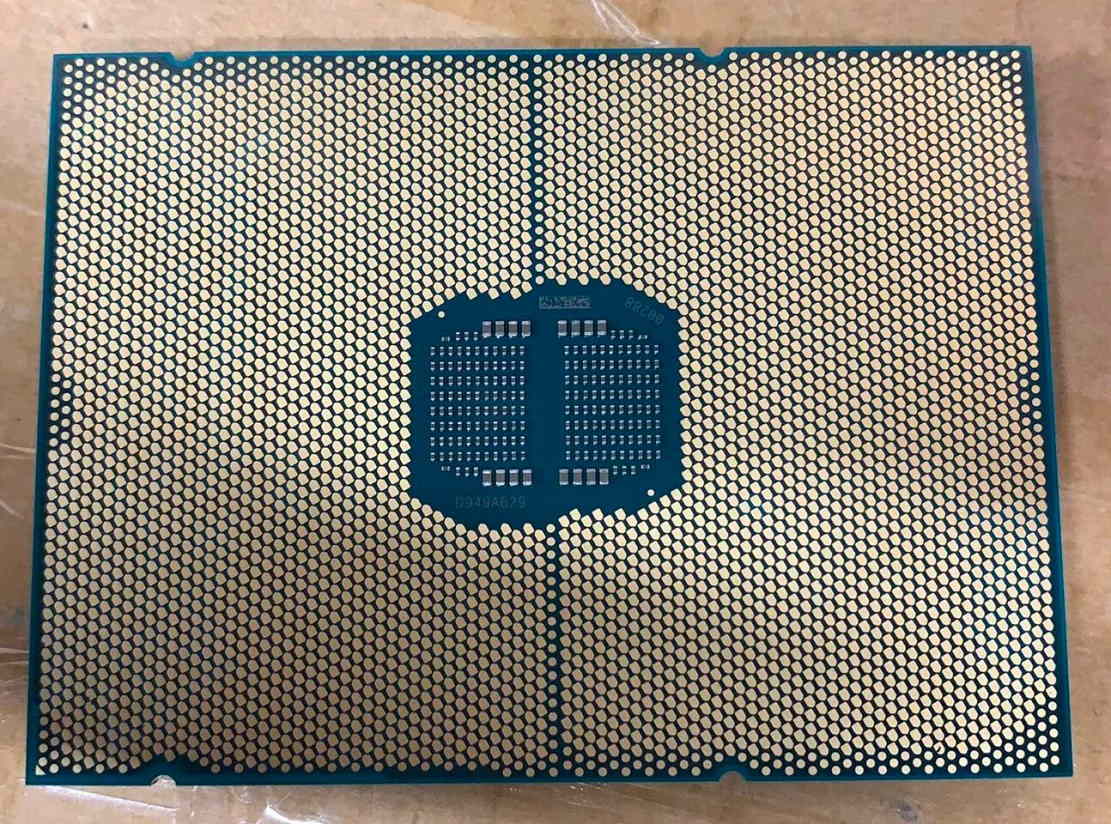

Unas imágenes filtradas nos han permitido ver con todo lujo de detalles el aspecto de un procesador Intel Sapphire Rapids Xeon, un chip de alto rendimiento para servidores, y gracias a esas imágenes podemos confirmar algo muy curioso: que Intel ha utilizado un diseño de encapsulado multi-chip, o MCM por sus siglas en inglés.

Si os fijáis bien en las imágenes os daréis cuenta de que este procesador Intel Sapphire Rapids Xeon está formado por dos matrices de núcleos, cada una de ellas está formada por 28 núcleos que pueden trabajar con un total de 56 hilos, lo que significa que suma, en conjunto, 56 núcleos y 112 hilos. Es una cifra impresionante, aunque todavía queda por detrás de los AMD EPYC de última generación, que suman 64 núcleos y 128 hilos, y que adoptan un diseño de módulo multi-chip, compuesto por un total de ocho pequeños encapsulados. Cada encapsulado contiene un chiplet con 8 núcleos, y están acompañados de un chip I/O que comunica con todos ellos.

He querido hacer esa descripción de ambos chips para que veáis las diferencias entre las dos arquitecturas que ha utilizado Intel. El Intel Sapphire Rapids Xeon no tiene un diseño de núcleo monolítico, es decir, no integra 56 núcleos en una única pastilla de silicio, pero tampoco recurre a la misma cantidad de pastillas de silicio que AMD para crear un procesador tope de gama. AMD logra 64 núcleos con ocho chiplets, Intel suma 56 núcleos con dos pastillas de silicio.

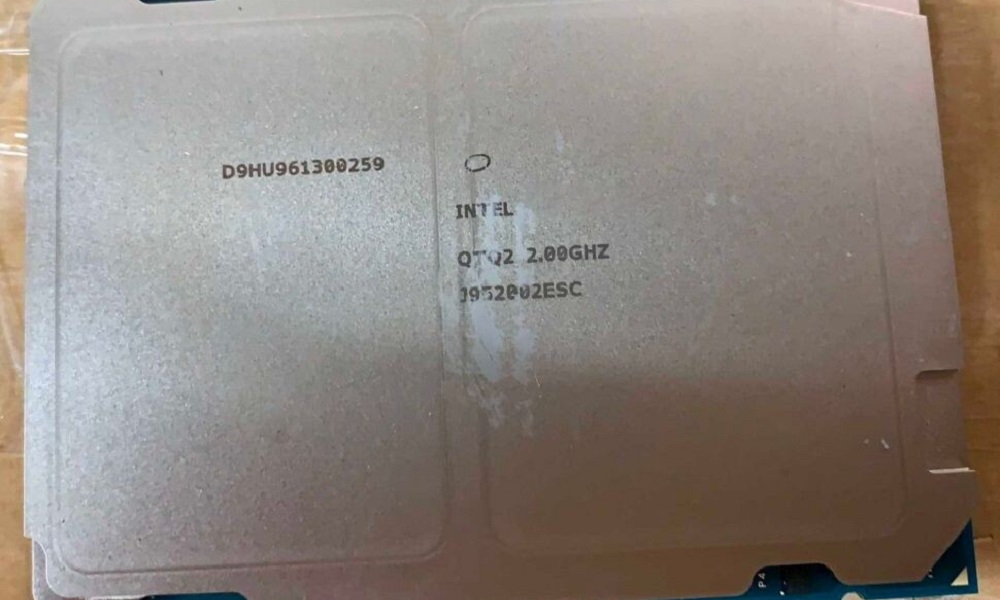

El Intel Sapphire Rapids Xeon está fabricado en proceso de 10 nm «SuperFin», el mismo que utilizan los procesadores Tiger Lake de Intel, utiliza el socket LGA4677 con 4.677 pines, y utiliza un EMIB para interconectar el silicio usando un intercalador activo.

Se espera que esta nueva generación de Intel ofrezca un aumento considerable del IPC, y que venga acompañada de novedades interesantes, entre las que podemos destacar el soporte de memoria DDR5 (sustituta de la DDR4, aunque todavía no se ha estandarizado), compatibilidad con el nuevo estándar PCIE Gen5, que ofrecerá una velocidad de transferencia de 32 GT/s, y que tenga soporte de CXL 1.1. Desconocemos sus frecuencias de trabajo finales, pero esta muestra de ingeniería funciona a 2 GHz.

Será interesante ver cómo compiten estos nuevos procesadores con los AMD EPYC Milan, que estarán basados en Zen 3, y que mantendrán el conteo de 64 núcleos y 128 núcleos, aunque con una mejora del IPC de un 15%.

-

A FondoHace 5 días

A FondoHace 5 díasHong Kong vuelve a marcar la agenda tecnológica global: InnoEX y Electronics Fair (Spring Edition) 2026

-

NoticiasHace 5 días

NoticiasHace 5 díasASUS presenta el ‘todo en uno’ para empresas, ExpertCenter P600 AIO

-

NoticiasHace 7 días

NoticiasHace 7 díasUn nuevo informe alerta de las brechas de seguridad en el desarrollo nativo de IA

-

NoticiasHace 5 días

NoticiasHace 5 díasApple Business, un servicio integral para empresas