Noticias

IBM y Rapidus quieren empezar a fabricar semiconductores a 2 nm en 2025

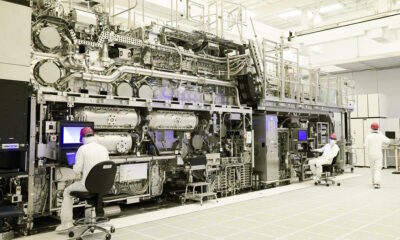

La competencia en el mundo de los semiconductores es feroz. TSMC es líder indiscutible si hablamos de fabricación de chips, ya que los diseños corren a cargo de sus clientes, pero IBM no está dispuesta a quedarse atrás en la carrera de los nanómetros, y ya tiene definida una estrategia para mejorar su posición en este sector, una alianza con la empresa japonesa Rapidus.

Esa alianza con el consorcio japonés de semiconductores Rapidus tendrá, como objetivo principal, establecer una línea de producción de chips en 2 nm en la primera mitad de 2025. Esa primera línea de producción trabajará con prototipos, lo que significa que no serán unidades comerciales, y que por tanto se trata de una fase de riesgo que representará una inversión muy importante para ambas empresas.

Si ese primer movimiento va bien, IBM y Rapidus se colocarán en una posición privilegiada dentro del sector de los semiconductores, y quedarán a la altura de TSMC, ya que la compañía taiwanesa también tiene previsto empezar a producir chips en el nodo de 2 nm para 2025, siempre que las cosas salgan según sus propias previsiones, obviamente.

Ahora mismo nos encontramos en una etapa de transición importante. El nodo de 5 nm es el más popular a día de hoy, pero el salto al nodo de 3 nm se convertirá muy pronto en una realidad, y este año dará comienzo su adopción por algunos gigantes del sector. Apple será, salvo sorpresa de última hora, la primera en lanzar un SoC para smartphones basado en el nodo de 3 nm de TSMC, el Apple A17, que será utilizado en los iPhone 15 Pro y iPhone 15 Pro Max.

Los saltos en el proceso de fabricación son importantes porque reducen el tamaño de los transistores, y hacen que sea posible introducir mejoras en el rendimiento y la eficiencia. También se consigue reducir el espacio ocupado en la oblea de silicio, lo que al final se traduce en una mayor cantidad de chips por oblea, con todo lo que ello supone en materia de costes de fabricación.

No obstante, al reducir el tamaño de los transistores las puertas lógicas se vuelven más delgadas, y esto hace que aumente el riesgo de que se produzcan fugas eléctricas. También resulta más complicado conseguir una buena tasa de éxito en la oblea, especialmente en diseños complejos, y esto se traduce en menos chips funcionales. El salto a los 2 nm podría ser muy complicado, ya que es un valor que nos acerca a los límites físicos del silicio, así que será interesante ver cómo avanza la industria en esa nueva aventura.

-

NoticiasHace 5 días

NoticiasHace 5 díasSAP duplica su adopción en la nube pública en las empresas de España en el último año

-

A FondoHace 4 días

A FondoHace 4 díasLos 12 principales cursos y certificaciones sobre IA generativa

-

NoticiasHace 7 días

NoticiasHace 7 díasCátedras Chip: ya es público el programa que quiere impulsar la industria del chip en España

-

A FondoHace 5 días

A FondoHace 5 díasHPE ProLiant Gen11 con AMD, las claves de su éxito