Noticias

AMD EPYC Bergamo, así será la CPU especializada en la nube

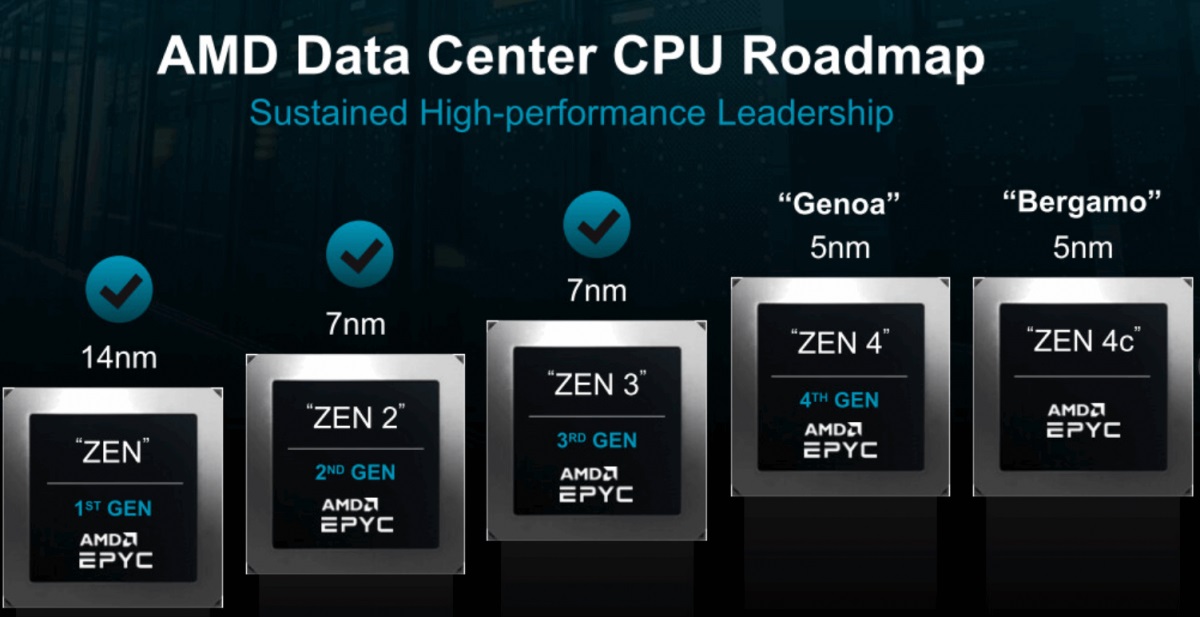

La compañía de Sunnyvale está trabajando en una nueva generación de procesadores especializados en la nube que, de momento, conocemos como EPYC Bergamo. Esta nueva serie estará basada en la arquitectura Zen 4c, una importante revisión de Zen 4 que, en líneas generales, adoptará cambios profundos para reducir el tamaño de los núcleos y aumentar la densidad de estos.

Para que tengáis una referencia, los procesadores AMD EPYC Genoa, basados en Zen 4, tienen una densidad de hasta 96 núcleos y 192 hilos por socket. Los EPYC Bergamo tendrían una configuración de hasta 128 núcleos y 256 hilos por socket, lo que significa que en una configuración de doble socket podríamos llegar a tener la friolera de 256 núcleos y 512 hilos. Sí, es realmente impresionante.

Al ser un procesador especializado en la computación en la nube su enorme capacidad de paralelización tiene mucho sentido, pero AMD también ha tenido muy en cuenta la eficiencia energética y el coste total de propiedad. Así, en vez de priorizar el rendimiento por núcleo se ha centrado en desarrollar una arquitectura con un enorme potencial multihilo, utilizando núcleos más sencillos a menor frecuencia de trabajo.

Zen 4c utilizará los núcleos Dionysus, que son un 35,4% más pequeños que los núcleos Zen 4, conocidos por el nombre en clave Persephone. Esta reducción de tamaño ha sido posible gracias a cuatro grandes claves:

- Reducción de las frecuencias de reloj en modo turbo de 3,7 GHz a 3,1 GHz, lo que permite que el empaquetado del enrutamiento de señal sea más denso y simplifica el proceso de determinación de la velocidad del chip (timing closure).

- Se ha reducido también el número de particiones físicas y se han acercado los clusters que contienen la parte lógica, lo que permite reducir el tamaño del encapsulado.

- AMD ha optado por utilizar celdas de SRAM 6T de doble puerto en vez de las celdas 8T. Esto hace que la memoria caché ocupe menos espacio en Zen 4c, aunque también implica que será más lenta que la caché de Zen 4.

- Se ha eliminado la matriz «through-silicon via» (TSV) utilizada en configuraciones de caché 3D.

El chiplet ha experimentado un profundo cambio en líneas generales, pero sin duda uno de los más interesantes es que Zen 4c ha doblado el número de núcleos por chiplet, que pasa de 8 a 16. Cada chiplet cuenta ahora con dos bloques CCX de ocho núcleos cada uno con 32 MB de caché L3 (16 MB por unidad CCX).

Los procesadores AMD EPYC Bergamo serán compatibles con memoria DDR5 en configuraciones de hasta 12 canales, vendrá con un nuevo chiplet que integrará todo el sistema I/O ofrecerá hasta 128 líneas PCIe Gen5. Su presentación debería producirse este mismo mes.

-

NoticiasHace 5 días

NoticiasHace 5 díasTelefónica España se alía con Sateliot para llevar comunicación 5G por satélite a sectores estratégicos

-

EntrevistasHace 4 días

EntrevistasHace 4 días«La mejor forma de acelerar la IA no es mover más datos, es llevar la IA allá donde están»

-

NoticiasHace 5 días

NoticiasHace 5 díasEl crecimiento del IoT obliga a reforzar la supervisión continua en los pagos digitales

-

NoticiasHace 4 días

NoticiasHace 4 díasSAP compra Dremio y Prior Labs para mejorar sus capacidades de IA