Noticias

AMD podría presentar Instinct MI200 y Milan-X el 8 de noviembre

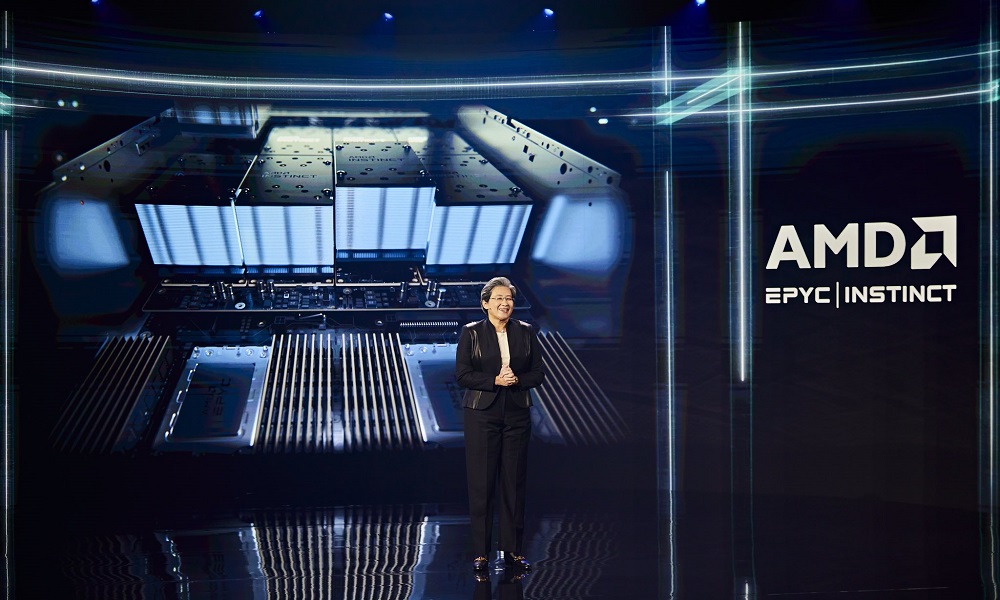

Lisa Su, CEO de AMD ha confirmado a través de Twitter que el próximo 8 de noviembre se celebrará un evento muy importante para la compañía de Sunnyvale, en el que la ejecutiva será la encargada de presentar las novedades más relevantes para el futuro, a corto y medio plazo, de AMD.

Aunque no ha entrado en detalles concretos sabemos, por filtraciones anteriores y por lo que se deduce de la imagen que ha compartido, que ese nuevo evento estará centrado alrededor de dos grandes claves, los aceleradores gráficos Instinct MI200, que utilizarán la arquitectura CDNA 2, y EPYC Milan-X, una nueva generación de procesadores para servidores que mantendrá el diseño MCM y la arquitectura Zen 3 como base, pero que vendrán con caché pilada en 3D.

Las aceleradoras Instinct MI200 podrían marcar una importante evolución en el sector porque, según las informaciones más recientes, serán las primeras en utilizar un diseño módulo multichip, lo que significa que sus GPUs ya no tendrán un diseño de núcleo monolítico, sino que combinarán varios chips para crear una «súper GPU». La idea es, en resumen, la misma que vimos con Zen y sus posteriores evoluciones, combinar chips pequeños con un número de núcleos relativamente bajo para crear configuraciones más potentes y con una mayor cantidad de núcleos.

En cuanto a los procesadores EPYC Milan-X, la novedad más importante ya la hemos comentado, sería la inclusión de caché L3 apilada en 3D, es decir, en vertical. El enfoque sería muy similar a lo que hemos visto, por ejemplo, con la memoria NAND Flash 3D, o con la memoria HBM, por poner dos ejemplos muy conocidos.

Cada procesador dentro de la serie Milan-X podría tener el doble, o quizá hasta el triple, de memoria caché L3 que las generaciones anteriores. Dicha memoria sirve como punto de apoyo para que la CPU almacene instrucciones y datos a los que necesita acceder con cierta frecuencia. Cuando la caché se llena, tiene que trasladar los nuevos datos e instrucciones a la memoria RAM. Dado que los accesos a la RAM son más lentos que a la caché, se produce una pérdida de rendimiento.

Pues bien, al contar con mayor memoria caché de tercer nivel, sería posible almacenar en ella más instrucciones y datos, y reducir la cantidad de peticiones necesarias a la RAM, lo que se traduciría en una mejora de rendimiento considerable. No puedo concretar todavía, ya que no tenemos datos específicos, pero me atrevería a pensar que ese extra de caché L3 podría impulsar el IPC entre un 10% y un 20%.

-

NoticiasHace 4 días

NoticiasHace 4 díasGoogle libera Gemma 4, su modelo de IA de código abierto más avanzado

-

NoticiasHace 5 días

NoticiasHace 5 díasASUS UGen300, el primer acelerador de IA en formato USB

-

ContentHace 3 días

ContentHace 3 díasNunsys Group convierte el dato en un activo estratégico para AIMPLAS

-

A FondoHace 2 días

A FondoHace 2 díasAnthropic lanza el Proyecto Glasswing para controlar la potencia de su propia IA en ciberataques