Noticias

AMD detalla su tecnología de caché 3D: El futuro pasa por apilar chips

Aprovechando el escenario de la HotChips, AMD ha dado más detalles sobre su tecnología de apilado de caché en 3D, conocida de forma provisional como AMD 3D V-Cache. Ya os habíamos hablado de ella anteriormente, y la verdad es que podría marcar un importante punto de inflexión en el sector, puesto que permitiría aumentar de manera notable el rendimiento sin tener que realizar renovaciones completas de arquitectura con tanta frecuencia.

Por si alguien no ha entendido bien el punto anterior, me explico. Para mejorar el rendimiento de una CPU es necesario renovar la arquitectura, y esta tiene que contar con las mejoras necesarias para permitir un aumento del IPC. Esto puede conseguirse de diferentes maneras, pero no debemos confundir un aumento de rendimiento mediante IPC con un aumento de rendimiento a través de fuerza bruta (aumento de núcleos o subida de frecuencias de trabajo). El segundo puede conseguirse sin necesidad de cambiar la arquitectura.

Con la caché 3D, AMD demostró que podía mejorar el rendimiento de un procesador en hasta un 15% sin tener que aumentar el número de núcleos, y sin alterar las frecuencias de trabajo ni el conteo de núcleos. Interesante, ¿pero por qué es necesario apilar la caché en 3D? Pues es muy sencillo, por una cuestión de espacio en el encapsulado. La implementación tradicional de la memoria caché se realiza en 2D, es decir, en el plano horizontal, lo que significa que esta acaba ocupando una cantidad considerable de espacio en el encapsulado, y que esto actúa como un límite físico incuestionable.

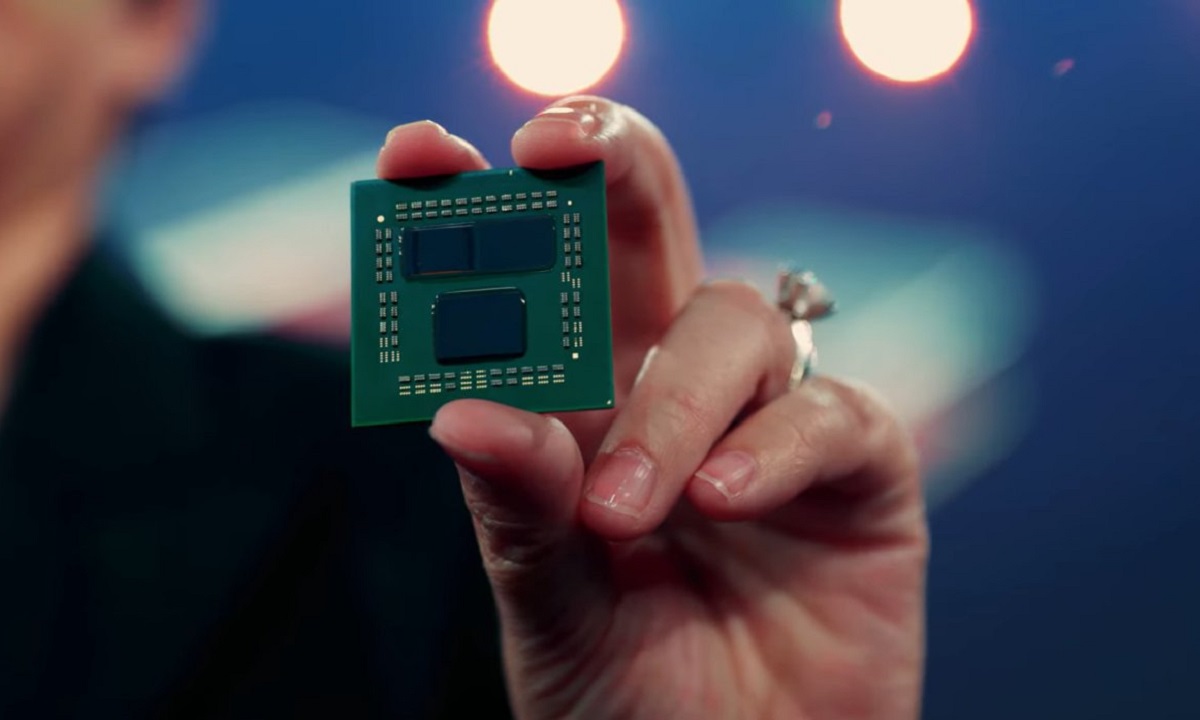

Al apilar en 3D, se utiliza el plano vertical, y el problema del espacio ocupado en el encapsulado desaparece. Gracias a ello, AMD pudo crear un procesador Ryzen 9 5900X con la friolera de 192 MB de caché L3, cuando la versión normal dispone de 64 MB de caché L3. La diferencia es enorme, y podría ser todavía mayor en futuras implementaciones, especialmente dentro de la serie EPYC.

Volviendo a la información que AMD ha dado en la HotChips, vemos que el apilado de caché en 3D se ha seguido, precisamente, para resolver los problemas del apilado en 2D. Sin embargo, apilar en 3D introduce otras complicaciones que hay que resolver, como por ejemplo el coste del encapsulado, la alimentación de las interconexiones para mantener ese apilado en 3D y los desafíos que presenta a nivel de ingeniería.

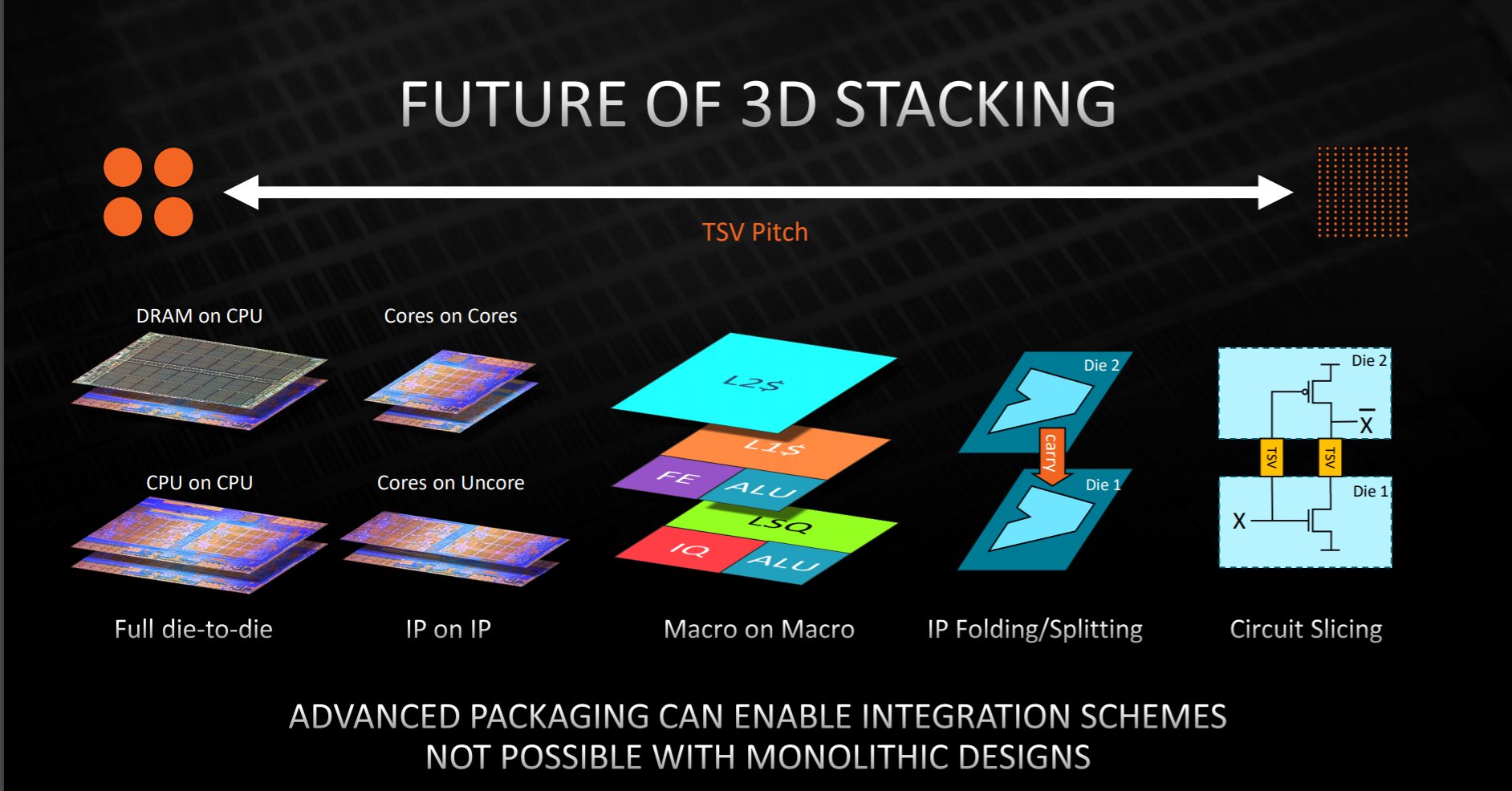

AMD utilizará un tipo de interconexión TSV (Through Silicon Via) con un micro salto de 9 micrones, que permitirá apilar caché 3D de forma eficiente, pero los planes de la compañía de Sunnyvale son mucho más ambiciosos. El objetivo final de la compañía que dirige Lisa Su es apilar diferentes encapsulados utilizando ese tipo de interconexión que trabaja a través del silicio. Esta estrategia supondrá una reinvención total del procesador tal y como lo conocemos, ya que hará posible el apilado de diferentes elementos en encapsulados diferentes, como la memoria RAM, núcleos sobre otros núcleos, GPU y otros.

-

NoticiasHace 5 días

NoticiasHace 5 díasGoogle libera Gemma 4, su modelo de IA de código abierto más avanzado

-

ContentHace 4 días

ContentHace 4 díasNunsys Group convierte el dato en un activo estratégico para AIMPLAS

-

NoticiasHace 6 días

NoticiasHace 6 díasASUS UGen300, el primer acelerador de IA en formato USB

-

A FondoHace 3 días

A FondoHace 3 díasAnthropic lanza el Proyecto Glasswing para controlar la potencia de su propia IA en ciberataques