Noticias

Samsung retrasa el proceso de 3 nm GAAFET

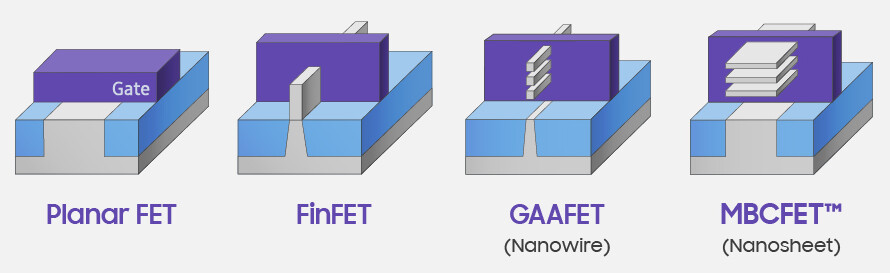

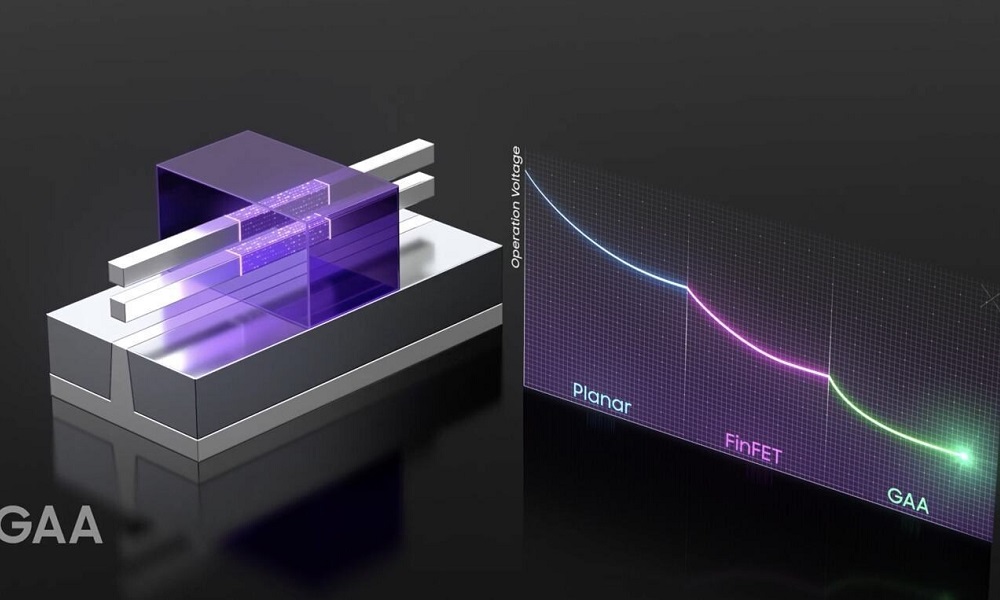

El pasado año os ofrecimos un anticipo del proceso de 3 nm de Samsung, basado en la tecnología GAAFET. Como recordarán nuestros lectores habituales, esas siglas se refieren a «Gate-All-Around FET», un modelo de diseño de transistores que traerá una serie de ventajas importantes, gracias a las cuales será posible completar el salto a un proceso que roza ya los límites teóricos del silicio.

Gracias al diseño GAAFET, el proceso de 3 nm de Samsung ofrecerá un control mejorado del canal de los transistores, y reducirá las fugas eléctricas. Este es, precisamente, uno de los problemas más importantes con los que hay que lidiar al reducir el proceso de fabricación de semiconductores, con las fugas eléctricas. Las puertas lógicas, que regulan el paso de la corriente eléctrica, se vuelven cada vez más delgadas cuando se pasa a un nodo inferior, lo que aumenta las posibilidades de que se produzcan fugas eléctricas. Obvia decir que, si esto ocurre, el proceso será inviable.

Samsung también dijo, en su momento, que piensa combinar este diseño con la tecnología «Multi Bridge Channel FET», y que gracias a ella podrá reducir el consumo de sus chips de 3 nm hasta en un 50%, y aumentar su rendimiento hasta en un 30%. Prometedor, sin duda, pero por desgracia este proceso se ha visto retrasado, según varias informaciones que TechPowerUP! ha recopilado en una sencilla explicación.

Dicha fuente indica que el proceso de 3 nm de Samsung basado en el diseño «Gate-All-Around FET» no llegará hasta 2024, y que esa sería la mejor fecha posible, lo que significa que todavía cabe la posibilidad de que se produzcan nuevos retrasos, y de que su lanzamiento se posponga a 2025, o incluso a una fecha posterior. Tened en cuenta que estas fechas se refieren a la entrada de dicho nodo en la fase de producción en masa, y no a etapas previas relacionadas con análisis y las pruebas para comprobar la viabilidad del proceso.

Por su parte, TSMC ha confirmado que espera tener listo su proceso de 2 nm en 2024. Dicho proceso utilizará litografía ultravioleta extrema de patrón múltiple, así como cobalto en contactos e interconexiones, canales reforzados con germanio y otras modificaciones a nivel interno que permitirán superar las limitaciones del silicio al llegar a ese proceso tan pequeño. Según los expertos, el techo del silicio está en 1,5 nm, aunque algunos creen que sería posible llegar a 1 nm. Cada vez queda menos para descubrir dónde está su auténtico límite.

-

NoticiasHace 5 días

NoticiasHace 5 díasGoogle libera Gemma 4, su modelo de IA de código abierto más avanzado

-

ContentHace 4 días

ContentHace 4 díasNunsys Group convierte el dato en un activo estratégico para AIMPLAS

-

A FondoHace 3 días

A FondoHace 3 díasAnthropic lanza el Proyecto Glasswing para controlar la potencia de su propia IA en ciberataques

-

NoticiasHace 6 días

NoticiasHace 6 díasASUS UGen300, el primer acelerador de IA en formato USB