Noticias

AMD EPYC Genoa bajo rayos X: 16 núcleos y 2 unidades CCD

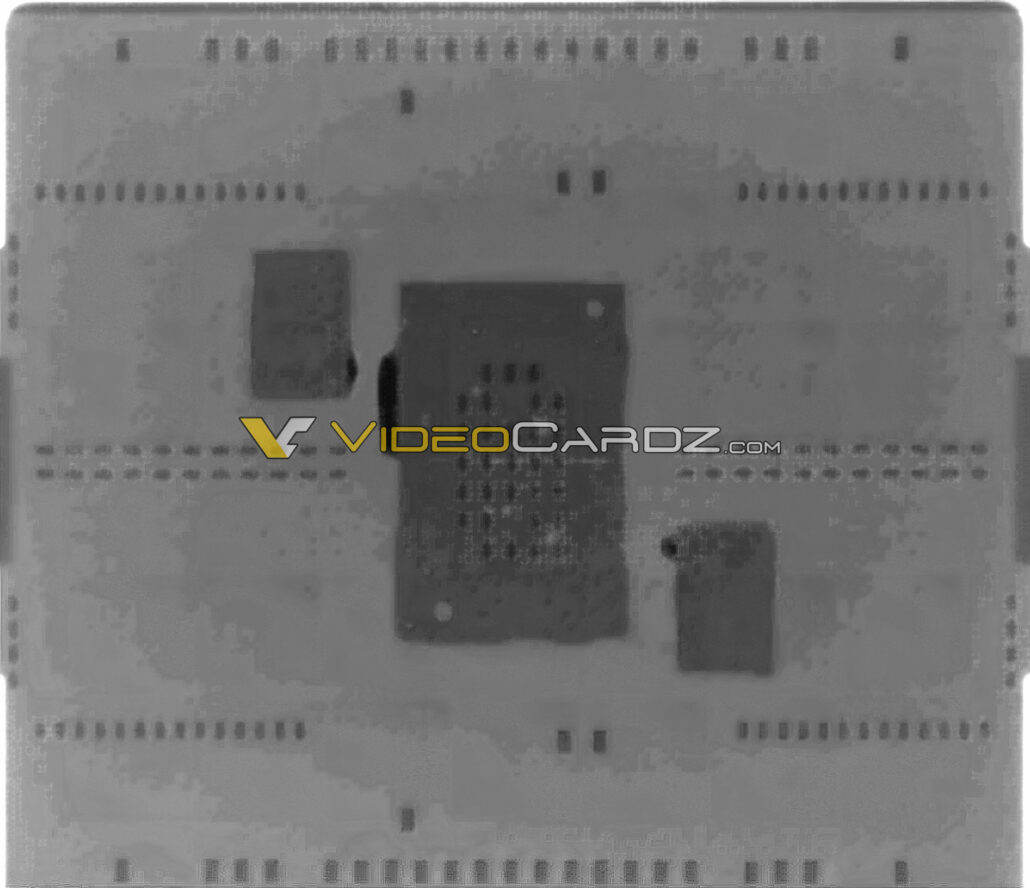

Una nueva filtración nos ha permitido ver un procesador EPYC Genoa de AMD de una manera nada habitual, y es que, gracias al uso de rayos X, ha sido posible descubrir qué se encuentra bajo ese enorme IHS (disipador de calor integrado) que vemos en la imagen de portada. Los conectores son, como cabía esperar, una matriz de contactos planos chapados en oro, lo que confirma el uso de un socket LGA, como ya habíamos comentado en ocasiones anteriores.

Toda la serie EPYC Genoa de AMD estará basada en la arquitectura Zen 4, así que la información que vamos a ver a continuación es muy importante porque ha sido tomada sobre una muestra temprana, lo que le confiere una validez indudable, y porque además nos permite confirmar algunas cosas que estaban en el aire, como la configuración exacta de núcleos e hilos por unidad CCD, también conocida popularmente como chiplet.

Este chip utilizará el nodo de fabricación de 5 nm de TSMC y contará, como vemos en la imagen adjunta, con dos unidades CCD, que son los rectángulos de menor tamaño. En el centro, tenemos el chip I/O, donde se integran, de forma externalizada, todos los elementos de interfaz, incluida la controladora de memoria DDR5. Dicho chip estará fabricado con el proceso de 6 nm de TSMC, según las últimas informaciones que tenemos.

Dado que el chip EPYC Genoa que se ha filtrado tendrá una configuración de 16 núcleos y 32 hilos, queda claro que cada una de esas unidades CCD tendrá un total de 8 núcleos y 16 hilos. Esto parece descartar, casi por completo, los rumores que aseguraban que, con el salto a Zen 4, AMD iba a empezar a utilizar unidades CCD con una configuración de 16 núcleos y 32 hilos.

La serie EPYC Genoa tendrá distintas configuraciones de núcleos e hilos, siendo la más potente la versión con 96 núcleos y 192 hilos. Esta estará equipada con un total de 12 unidades CCD, sumará un total de 384 MB de memoria caché L3, será compatible con memoria DDR5 y también con la interfaz PCIE Gen5, lo que significa que supondrá un salto importante tanto a nivel de rendimiento en bruto, por IPC y por aumento de núcleos, como a nivel de plataforma. Su lanzamiento está previsto para mediados de este mismo año, aunque todavía no tenemos una fecha exacta, así que toca esperar.

-

NoticiasHace 4 días

NoticiasHace 4 díasGoogle libera Gemma 4, su modelo de IA de código abierto más avanzado

-

ContentHace 3 días

ContentHace 3 díasNunsys Group convierte el dato en un activo estratégico para AIMPLAS

-

NoticiasHace 6 días

NoticiasHace 6 díasSiete pecados capitales que exponen a las Pymes a ciberataques

-

NoticiasHace 5 días

NoticiasHace 5 díasASUS UGen300, el primer acelerador de IA en formato USB