Noticias

TSMC celebrará un evento especial dedicado al proceso de 3 nm

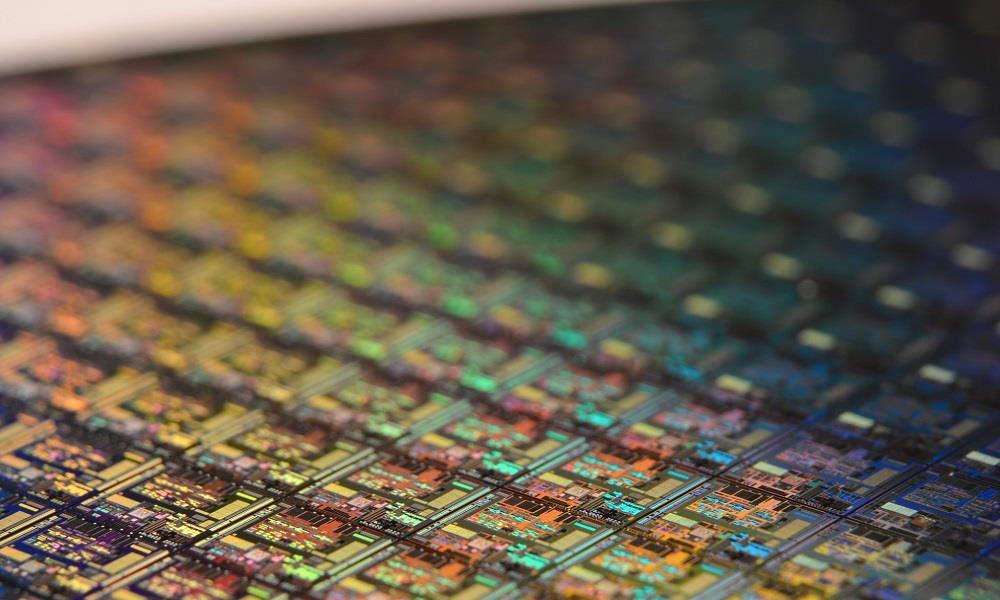

El gigante taiwanés está imparable. TSMC ha confirmado recientemente que ha suministrado mil millones de obleas en proceso de 7 nm, un dato que reafirma su posición como uno de los mayores fabricantes de semiconductores del mundo, y también ha reiterado que sus planes van según lo previsto en lo que respecta a los procesos de 5 nm y 3 nm.

Sobre el proceso de 5 nm, TSMC ha comentado que los envíos alcanzarán un volumen óptimo (envíos en masa) a partir de finales de este mismo año, lo que nos lleva a pensar directamente en el cuarto trimestre de 2020. Este proceso jugará un papel muy importante dentro del sector smartphone, ya que tanto los nuevos SoCs de Apple (serie A14) y de Qualcomm (Snapdragon 875) estarán fabricados en dicho proceso.

Huawei no podrá acceder al proceso de fabricación de 5 nm debido al veto de Estados Unidos, y dadas las complejidades que este presenta es fácil entender que la compañía china esté considerando tirar la toalla y dejar de diseñar sus propios chips. No tendría sentido recurrir a otras fábricas que te obligarán a diseñar un chip en un proceso que ya no es competitivo.

En cuanto al proceso de 3 nm, sucesor del proceso de 5 nm y previsto para 2022, TSMC ha dicho que tiene previsto celebrar un evento especial el próximo 25 de agosto donde ofrecerán más detalles sobre este, y también sobre los procesos que le permitirán fabricar semiconductores en procesos inferiores a los 3 nm. No ha dado detalles, pero está claro que será un evento de gran importancia.

Creo que es importante recordar que cuando hablamos del proceso de 3 nm nos movemos muy cerca de los límites teóricos del silicio. Esto se debe, principalmente, al tema de la reducción del grosor de las puertas lógicas que implica el salto a un proceso más pequeño, y las dificultades que hay que afrontar para evitar las fugas eléctricas con esas puertas lógicas más delgadas. Un chip que no puede cambiar de estado de forma controlada y que tiene fugas eléctricas es un chip no funcional, así de simple.

Las reducciones graduales de proceso de fabricación son viables hasta un cierto punto, y estamos cada vez más cerca de llegar al límite del silicio. Es probable que, para bajar de los 3 nm, se haga necesario adoptar nuevos materiales que puedan compensar las limitaciones inherentes al silicio, aunque todavía no tenemos claro qué camino piensa tomar TSMC en este sentido.

-

NoticiasHace 5 días

NoticiasHace 5 díasGoogle libera Gemma 4, su modelo de IA de código abierto más avanzado

-

ContentHace 4 días

ContentHace 4 díasNunsys Group convierte el dato en un activo estratégico para AIMPLAS

-

NoticiasHace 6 días

NoticiasHace 6 díasASUS UGen300, el primer acelerador de IA en formato USB

-

A FondoHace 3 días

A FondoHace 3 díasAnthropic lanza el Proyecto Glasswing para controlar la potencia de su propia IA en ciberataques