Noticias

Western Digital apuesta por RISC-V impulsando el chip Open Source

Western Digital ha presentado esta semana en el congreso RISC-V Summit tres innovaciones para la arquitectura libre y abierta creada en el mundo académico por investigadores de la prestigiosa Universidad de Berkeley y que está considerado el proyecto de chip Open Source más prometedor de la industria.

La presentación de WD, primer fabricante mundial de discos duros y uno de los grandes del almacenamiento, incluyó un nuevo núcleo de código abierto RISC-V denominado ‘SweRV’. Un procesador que la compañía usará en sus controladores para SSDs y que espera «impulse el desarrollo de nuevas aplicaciones centradas en datos para la Internet de las Cosas, procesamiento seguro, controles industriales y otros».

WD también anunció el «OmniXtend», un nuevo enfoque abierto para proporcionar memoria caché coherente sobre un tejido Ethernet. Es una arquitectura de sistema centrada en la memoria que proporciona interfaces abiertas para el acceso y el intercambio de datos en diferentes tipos de procesadores, incluidos CPU, GPU, aceleradores de aprendizaje automático, FPGA y otros. La solución OmniXtend también ofrece soporte para futuras estructuras avanzadas que conectan componentes de computación, almacenamiento, memoria y E / S.

El tercero de los anuncios y como el resto de fuente abierta, ha sido ‘SweRV Instruction Set Simulator’ (ISS), un programa que simula la ejecución de instrucciones en el procesador SweRV. WD utilizó la ISS para validar el diseño del núcleo de SweRV con más de 10 mil millones de instrucciones ejecutadas. WD espera que el núcleo SweRV y su simulador avancen en la adopción del código abierto RISC-V ISA.

RISC-V: impulsando el chip Open Source

Western Digital es uno de los miembros fundadores de la Fundación RISC-V. Creada en 2015, la organización incluye empresas como AMD, Google, IBM, NVIDIA, NXP y Qualcomm. Su objetivo es muy ambicioso y trata de impulsar un chip Open Source de alcance masivo que garantice la seguridad y la compatibilidad con las aplicaciones actuales como alternativa a plataformas tan asentadas como x86 y ARM.

La clave es RISC-V (ISA), una arquitectura libre y abierta creada en el mundo académico por investigadores de la prestigiosa Universidad de Berkeley y actualmente la propuesta más clara para conseguir el pretendido chip Open Source.

Comparte las mismas raíces RISC que otras arquitecturas como ARMv8, puede manejar Linux y otros sistemas operativos de 32, 64 y 128 bits, y puede utilizarse como procesadores de propósito general o especializados. Como no utiliza las técnicas de ejecución especulativa está libre de las vulnerabilidades tipo Meltdown y Spectre.

Creado en 2010, su desarrollo está en pañales frente a los gigantes del sector, pero -dicen los técnicos- que su potencial es enorme, como muestran los ataques que le han llovido desde la misma ARM y a los que se opusieron su mismo personal y las grandes corporaciones que apoyan RISC-V.

Recientemente, el consorcio tecnológico sin ánimo de lucro Linux Foundation, anunció un acuerdo de colaboración con la Fundación RISC-V para promover la adopción de un chip Open Source. Un chip abierto que cualquier foundry de semiconductores pudiera producir para cualquier fabricante, con base en unas especificaciones abiertas sin la necesidad de concesión de licencias de propiedad intelectual y que permitiera mejoras y correcciones a través de los esfuerzos de la comunidad a medida que surgieran nuevas necesidades. O problemas tan enormes como Meltdown y Spectre que solo se podrán solucionar por completo con nuevos diseños.

El anuncio de la Linux Foundation es otro espaldarazo teniendo en cuenta que es la organización más importante en el fomento de Linux. El objetivo es juntar las comunidades de Linux y RISC-V para mejorar la adopción de este chip Open Source y el acuerdo de colaboración se concretará en programas de capacitación, desarrollo de herramientas, apoyo de marketing y asesoría legal.

-

NoticiasHace 4 días

NoticiasHace 4 díasGoogle libera Gemma 4, su modelo de IA de código abierto más avanzado

-

ContentHace 3 días

ContentHace 3 díasNunsys Group convierte el dato en un activo estratégico para AIMPLAS

-

NoticiasHace 5 días

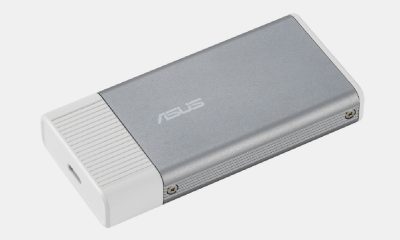

NoticiasHace 5 díasASUS UGen300, el primer acelerador de IA en formato USB

-

NoticiasHace 6 días

NoticiasHace 6 díasSiete pecados capitales que exponen a las Pymes a ciberataques