Noticias

El coste de las CPUs y GPUs seguirá subiendo a pesar de los saltos de nodo

Los saltos en los procesos de fabricación son muy importantes porque, como ya sabrán muchos de nuestros lectores, permiten reducir el tamaño de los transistores y aumentar la densidad de los mismos. También permiten la introducción de optimizaciones en el diseño que al final se traducen en mejoras de rendimiento y la eficiencia. CPUs y GPUs son dos de los tipos de chips que más se benefician de los saltos a nuevos procesos de fabricación, pero esta realidad está empezando a cambiar.

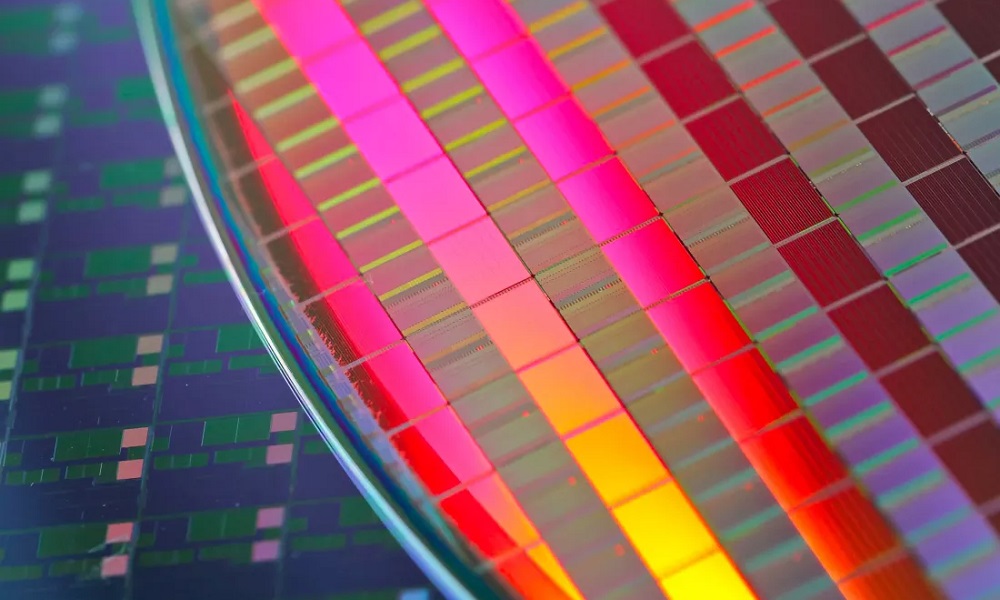

Según TSMC, el fabricante de semiconductores más importante del mundo, los transistores de la memoria SRAM que se utiliza en las cachés de CPUs y GPUs está dejando de escalar con cada salto de nodo, es decir, no se está reduciendo el tamaño de sus transistores, y esto es un problema por muchas razones. La primera está en el espacio ocupado a nivel de silicio, y es que una caché con el mismo tamaño de transistores en CPUs y GPUs que tienen transistores cada vez más pequeños abarca una cantidad de espacio enorme en comparación con el resto de elementos.

Por otro lado, también tenemos dos problemas importantes, no se consiguen los mismos beneficios al saltar a un nodo más avanzado, y los costes de producción aumentan porque el impacto en la oblea sigue siendo alto, debido a esa cuestión de tamaño que ya hemos mencionado (sus transistores siguen siendo igual de grandes aunque se utilice un nodo más avanzado y caro, y ocupan el mismo espacio en la oblea de silicio).

Para los grandes del sector esto podría convertirse en un obstáculo importante que no solo encarecerá futuros diseños, ya que al final tanto las CPUs como las GPUs utilizan memorias caché de distintos niveles, sino que además impedirá que ciertas arquitecturas puedan llegar a su pico máximo de miniaturización, ya que la caché seguirá siendo «enorme» en comparación.

TSMC ya ha confirmado que la memoria SRAM fabricada con el nodo de 3 nm tendrá la misma densidad de transistores que la memoria SRAM fabricada en el nodo de 5 nm, que es precisamente el que se utiliza en los procesadores Ryzen 7000 de AMD. El nodo de 3 nanómetros mejorado, conocido como N3B, tampoco pinta un panorama mucho mejor, ya que solo será capaz de reducir el tamaño de los transistores de la SRAM en un 5%.

En la gráfica adjunta podemos ver el escalado de los diferentes nodos de TSMC aplicados a la SRAM, y deja claras dos cosas, que el salto del nodo de 7 nm al de 5 nm representó una mejora muy pequeña en la reducción del área ocupada, y también ese estancamiento que sufriremos con el salto a los 3 nm. Si continuamos la tendencia actual, la memoria SRAM tendrá una densidad de transistores cada vez mayor, pero estos no se reducirán de tamaño lo suficientemente rápido, y ocuparán cada vez más espacio.

AMD ya ha tomado cartas en el asunto en este sentido, y es que no es casualidad que la caché infinita de sus tarjetas gráficas Radeon RX 7900 XT y XTX haya sido externalizada a 6 chiplets. Esto ha evitado tener que integrarlos en la GPU, algo que habría dado como fruto un chip enorme.

-

NoticiasHace 4 días

NoticiasHace 4 díasGoogle libera Gemma 4, su modelo de IA de código abierto más avanzado

-

ContentHace 3 días

ContentHace 3 díasNunsys Group convierte el dato en un activo estratégico para AIMPLAS

-

NoticiasHace 6 días

NoticiasHace 6 díasSiete pecados capitales que exponen a las Pymes a ciberataques

-

NoticiasHace 5 días

NoticiasHace 5 díasASUS UGen300, el primer acelerador de IA en formato USB